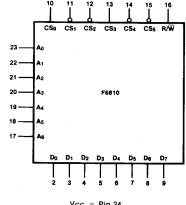

# F6810/F68A10/F68B10 128 x 8-Bit Static Random Access Memory

Microprocessor Product

### Description

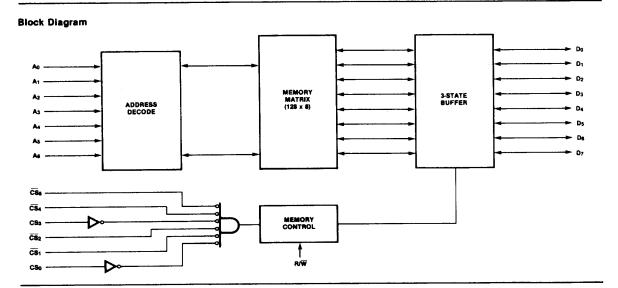

The F6810 128 x 8-bit static RAM is a byte-organized memory designed for use in bus-organized systems. Fabricated with n-channel, silicon-gate technology, the device is available in three frequency ranges: 1.0 MHz (F6810), 1.5 MHz (F68A10), 2.0 MHz (F68B10). The device, which operates from a single power supply, is compatible with TTL and DTL; it needs no clocks or refreshing because of its static operation.

The memory is compatible with the F6800 microcomputer family, providing random storage in byte increments. Memory expansion is provided through multiple chip select inputs.

- Organized as 128 Bytes of 8 Bits

- Static Operation

- Bidirectional 3-State Data Input/Output

- Six Chip Select Inputs (Four Active LOW, Two Active HIGH)

- Single +5 V Power Supply

- TTL-Compatible

- Maximum Access Time: 450 ns for F6810 360 ns for F68A10 250 ns for F68B10

### Pin Names

D<sub>0</sub>-D<sub>7</sub> A<sub>0</sub>-A<sub>6</sub> CS<sub>0</sub>-CS<sub>5</sub> R/W Bidirectional Data Bus Address Inputs Chip Select Inputs Read/Write Input

### **Logic Symbol**

V<sub>CC</sub> = Pin 24 V<sub>SS</sub> = Pin 1

# Connection Diagram 24-Pin DIP

(Top View)

### F6810/F68A10/F68B10

| Signal Function Descriptions     |            |                |                                                                                                                                           |  |  |  |

|----------------------------------|------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Mnemonic                         | Pin<br>No. | Name           | Description                                                                                                                               |  |  |  |

| Bus Handsha                      | ke         |                |                                                                                                                                           |  |  |  |

| A <sub>0</sub> -A <sub>6</sub>   | 17-23      | Address<br>Bus | Input signal lines containing address to which data is to be written or from which data is to be read                                     |  |  |  |

| D <sub>0</sub> -D <sub>7</sub>   | 2-9        | Data<br>Bus    | Bidirectional input/<br>output signal lines over<br>which data is read from<br>or written to the device                                   |  |  |  |

| Chip Control                     |            |                |                                                                                                                                           |  |  |  |

| CS <sub>0</sub> -CS <sub>5</sub> | 10-15      | Chip<br>Select | Input signal lines that prepare the device for a read or write operation                                                                  |  |  |  |

| R/₩                              | 16         | Read/<br>Write | Input signal lines that<br>selects a chip read or<br>write operation; a HIGH<br>selects memory read,<br>and a LOW selects<br>memory write |  |  |  |

| Supply<br>V <sub>SS</sub>        | 1          | Ground         | Ground for supply and signals                                                                                                             |  |  |  |

Vcc

24

| Absolute Maximum Ratings             |                   |

|--------------------------------------|-------------------|

| Supply Voltage                       | - 0.3 V, + 7.0 V  |

| Input Voltage                        | - 0.3 V, + 7.0 V  |

| Operating Temperature - TL, TH       |                   |

| F6810, F68A10, F68B10                | 0°C, +70°C        |

| F6810C, F68A10C                      | − 40 °C, + 85 °C  |

| F6810DM                              | - 55 °C, + 125 °C |

| Storage Temperature Range            | -65°C, +150°C     |

| Thermal Resistance - θ <sub>JA</sub> | 82.5 °C/W         |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages.

These are stress ratings only, and functional operation at these ratings, or under any conditions above those indicated in this data sheet, is not implied. Exposure to the absolute maximum rating conditions for extended periods of time may affect device reliability, and exposure to stresses greater than those listed may cause permanent damage to the device.

| Recommended | Operating Condit | ions |

|-------------|------------------|------|

|             |                  |      |

| Symbol | Characteristic     | Min   | Тур | Max  | Unit |

|--------|--------------------|-------|-----|------|------|

| Vcc    | Supply Voltage     | 4.75  | 5.0 | 5.25 | V    |

| ViH    | Input HIGH Voltage | 2.0   |     | 5.25 | ٧    |

| ViL    | Input LOW Voltage  | - 0.3 |     | 0.8  | V    |

Supply +5 V supply voltage

## F6810/F68A10/F68B10

DC Characteristics  $V_{CC}$  = 5.0 V  $\pm 5\%$ ,  $V_{SS}$  = 0,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted.

| Symbol           | Characteristic                         | Min | Тур | Max       | Unit | Conditions                                                                                            |

|------------------|----------------------------------------|-----|-----|-----------|------|-------------------------------------------------------------------------------------------------------|

| IIN              | Input Current (An, R/W, CSn, CSn)      |     |     | 2.5       | μΑ   | V <sub>IN</sub> = 0 to 5.25 V                                                                         |

| Voh              | Output HIGH Voltage                    | 2.4 |     |           | V    | loн = -205 μA                                                                                         |

| V <sub>OL</sub>  | Output LOW Voltage                     |     |     | 0.4       | ٧    | loL = 1.6 mA                                                                                          |

| ILO              | Output Leakage Current, 3-State        |     |     | 10        | μΑ   | $\overline{CS} = 0.8 \text{ V or } \overline{CS} = 2.0 \text{ V},$<br>V <sub>O</sub> = 0.4 V to 2.4 V |

| lcc <sup>1</sup> | Supply Current F6810<br>F68A10, F68B10 |     |     | 80<br>100 | mA   | V <sub>CC</sub> = 5.25 V, all other pins grounded, T <sub>A</sub> = 0 °C                              |

| CIN              | Input Capacitance                      |     |     | 7.5       | ρF   | f = 1.0 MHz,                                                                                          |

| Cout             | Output Capacitance                     |     |     | 12.5      | pF   | T <sub>A</sub> = 25°C                                                                                 |

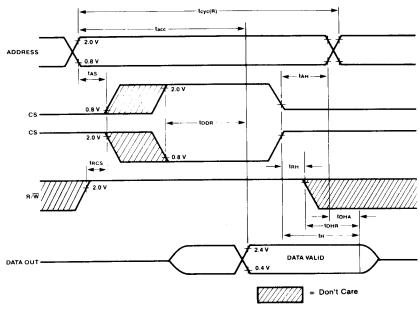

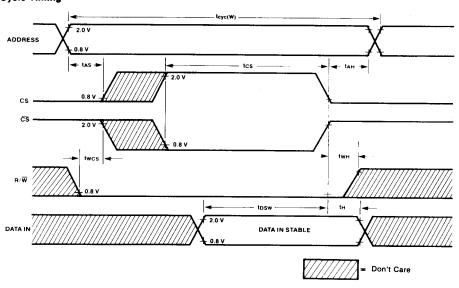

Bus Timing Characteristics  $V_{CC}$  = 5.0 V  $\pm 5\%$ ,  $V_{SS}$  = 0,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted.

| Symbol              | Characteristic                  | F6810 |     | F68A10 |     | F68B10 |          | Unit |  |

|---------------------|---------------------------------|-------|-----|--------|-----|--------|----------|------|--|

| Syllibol            | Characteristic                  | Min   | Max | Min    | Max | Min    | Max      | 7 "" |  |

| Read (Figu          | ure 1)                          |       |     |        |     |        |          |      |  |

| t <sub>cyc(R)</sub> | Read Cycle Time                 | 450   |     | 360    |     | 250    |          | ns   |  |

| tacc                | Access Time                     |       | 450 |        | 360 |        | 250      | ns   |  |

| tas                 | Address Set-up Time             | 20    |     | 20     |     | 20     |          | ns   |  |

| tah                 | Address Hold Time               | 0     |     | 0      |     | 0      |          | ns   |  |

| t <sub>DDR</sub>    | Data Delay Time (Read)          |       | 230 |        | 220 |        | 180      | ns   |  |

| t <sub>RCS</sub>    | Read-to-Select Delay Time       | 0     |     | 0      |     | 0      |          | ns   |  |

| t <sub>DHA</sub>    | Data Hold from Address          | 10    |     | 10     |     | 10     |          | ns   |  |

| t <sub>H</sub>      | Output Hold Time                | 10    |     | 10     |     | 10     |          | ns   |  |

| t <sub>DHR</sub>    | Data Hold from Read             | 10    | 80  | 10     | 60  | 10     | 60       | ns   |  |

| t <sub>RH</sub>     | Read Hold from Chip Select      | 0     |     | 0      |     | 0      |          | ns   |  |

| Write (Figu         | ure 2)                          |       |     |        |     |        | .*.      |      |  |

| t <sub>cyc(W)</sub> | Write Cycle Time                | 450   |     | 360    |     | 250    |          | ns   |  |

| tas                 | Address Set-up Time             | 20    |     | 20     |     | 20     | 1        | ns   |  |

| t <sub>AH</sub>     | Address Hold Time               | 0     |     | 0      |     | 0      |          | ns   |  |

| tcs                 | Chip Select Pulse Width         | 300   |     | 250    |     | 210    |          | ns   |  |

| twcs                | Write-to-Chip Select Delay Time | 0     |     | 0      |     | 0      |          | ns   |  |

| t <sub>DSW</sub>    | Data Set-up Time (Write)        | 190   |     | 80     |     | 60     | <u> </u> | ns   |  |

| t <sub>H</sub>      | Input Hold Time                 | 10    |     | 10     |     | 10     |          | ns   |  |

| twn                 | Write Hold from Chip Select     | 0     |     | 0      |     | 0      | 1        | ns   |  |

Fig. 1 Read Cycle Timing

Note CS and  $\overline{\text{CS}}$  can be enabled for consecutive read cycles, provided  $\overline{\text{RW}}$ remains at VIH.

Fig. 2 Write Cycle Timing

#### Note

CS and  $\overline{\text{CS}}$  can be enabled for consecutive write cycles, provided  $R\overline{\text{W}}$  is strobed to V<sub>IH</sub> before or coincident with the address change, and remains HIGH for time t<sub>AS</sub>.

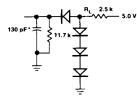

## Fig. 3 Output Load

\*Includes jig capacitance

## **Timing Conditions**

The conditions under which the timing characteristics have been determined are as follows:

Input Pulse Levels

Input Rise and Fall Times

Output Load

Vcc

Vss

TA

20 ns See Figure 3 5.0 V  $\pm$ 5% 0 T<sub>L</sub> to T<sub>H</sub>, unless otherwise noted

0.8 V to 2.0 V

## F6810/F68A10/F68B10

## Ordering Information

| Speed   | Order Code  | Temperature Range |

|---------|-------------|-------------------|

| 1.0 MHz | F6810P,S    | 0°C to 70°C       |

|         | F6810CP,CS  | -40°C to +85°C    |

|         | F6810DM     | -55°C to +125°C   |

| 1.5 MHz | F68A10P,S   | 0°C to +70°C      |

| ļ       | F68A10CP,CS | -40°C to +85°C    |

| 2.0 MHz | F68B10DM    | -55°C to +125°C   |

| . —     | F68B10P,S   | 0°C to +70°C      |

P = Plastic package, S = Ceramic package